電子機器開発における2大テーマ「EMCと熱」課題解決への第一歩

皆さま、こんんちは。

IDAJの金澤です。

電子機器の高性能化・小型化・高密度化が進む中で、電磁両立性(EMC:Electromagnetic Compatibility)と熱設計は、製品開発における最重要課題の一つです。これらは単なる設計要素ではなく、製品の信頼性・性能、さらには市場投入までのスピードを左右する決定的な要因となりえます。

EMCと熱は、互いに独立した課題のように見えて、実際には密接に関係しています。例えば、ノイズ対策のために導入したシールドやフィルタが放熱経路を阻害し、逆に冷却性能を高めるために追加した金属部材が予期せぬ放射ノイズを生むことがあります。すなわち、ノイズ対策と冷却設計はトレードオフの関係にあり、両者をバランス良く最適化することが必要です。

電子機器開発におけるEMC問題

電子機器の開発において、EMC(電磁両立性)は避けては通れない課題の一つで、CISPR・IEC・ISOといった国際規格をはじめ、米国のFCC、欧州のCEマーキング、日本のVCCIなど、地域ごとに厳格な認証基準が定められています。これらの規格に適合しなければ市場投入できないため、開発段階でのEMC対策は極めて重要です。しかし現実には、設計段階で想定していなかったノイズ経路や共振現象が生じ、規格を満たせずに試作段階のEMC試験で「NG」となるケースが少なくありません。この場合、原因の特定から対策立案、再試験までに数日から数か月を要する可能性があり、開発スケジュール全体に大きな影響を及ぼします。

EMC対策としては、以下のような部品や手法が主に用いられます。

- フィルタリング:コンデンサ、フェライトコア、チョークコイルなどによるノイズ抑制

- シールディング:ケーブルシールド、導電テープ、電磁波吸収シートなどによる遮蔽

- グラウンディング:ストラップやクランプを用いた接地処理

しかし、どの対策が有効かを見極めるには時間と試行錯誤が必要で、「原因は何か」「どの対策が効くか」を見通すことは容易ではありません。結果として、再設計や測定準備にかかる人件費、試作費・対策部材費、暗室利用料、外部認証機関への再依頼費用、さらには販売機会損失といった多大なコストが発生します。加えて、EMC問題は「外部への放射」だけでなく、機器内部での自家中毒、すなわち自装置内のノイズが自らの回路に悪影響を与えるケースも見られ、高速デジタル回路が発する基板ノイズがCPUなどの被害回路に干渉することで、誤動作や通信エラーを引き起こすことがあります。

このように、EMC問題は単なる試験対応だけの問題ではなく、製品開発全体のコストとスケジュールに直結するリスク要因であり、早期の予測および解析・設計段階での最適化が求められます。

電子機器開発におけるEMC問題

CAEを使ったEMC検証の現状

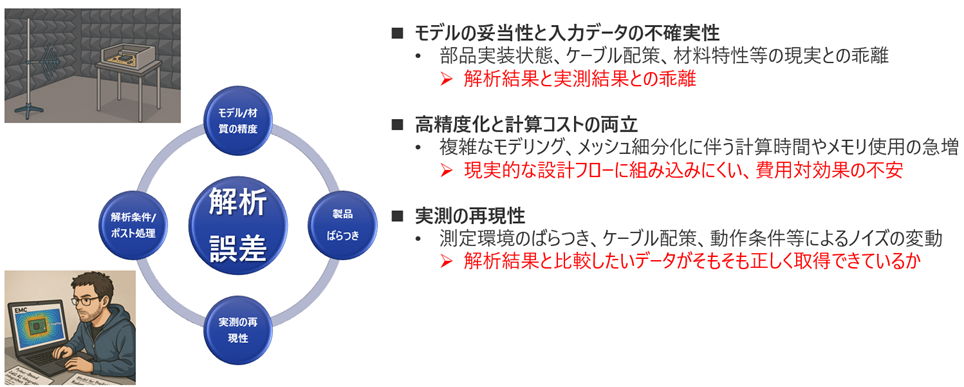

近年、電子機器のEMC設計においても、CAEによる電磁界シミュレーションが広く活用されているのはご承知の通りです。実機試験に先立ってノイズ源や放射経路を把握できる点が大きなメリットですが、現実の設計開発フローでは、依然としていくつかの課題を抱えています。

(1)モデルの妥当性と入力データの不確実性

CAEによる解析結果の信頼性は、モデルの正確さと入力データの品質に大きく依存します。しかし実際の開発現場では、部品の実装状態、ケーブル配策、材料の特性などが解析モデルに正確に反映されないケースが多く、これが解析結果と実測結果の乖離を引き起こします。特に、筐体内の結合構造や微細なグラウンド経路など、実装条件が結果に大きく影響する部分の再現が難しい点が課題です。

(2)高精度化と計算コストの両立

EMCシミュレーションの高精度化では、モデルの複雑化やメッシュの微細化が避けられず、結果として計算時間やメモリ使用量が急増します。これにより、1ケースの解析でも数時間から数日を要することがあり、現実的な設計サイクルに組み込みにくいという問題が生じます。また、解析コストが増大することで、費用対効果の面でも不安が残ります。精度と効率の両立が、EMC解析の実運用における重要なテーマとなっています。

(3)実測との再現性の確保

シミュレーション結果を評価するには、実測との比較が不可欠です。しかし、暗室の反射条件などの測定環境のばらつき、ケーブルの取り回し、動作状態の違いなどによって、同じ機器でも測定ごとに結果が異なることがあります。そのため、解析結果が誤っているのか、測定データ自体が正確に取得できていないのかを判断することが難しく、モデルと実機の対応付けが大きな課題です。

CAEを使ったEMC検証の現状

このように、CAEによるEMC検証は高い可能性を持つ一方で、モデルの信頼性、計算効率、実測再現性という課題があります。これらの課題を解決すべく、実測データと解析技術を融合したアプローチをご提案します。

EMC検証アプローチ

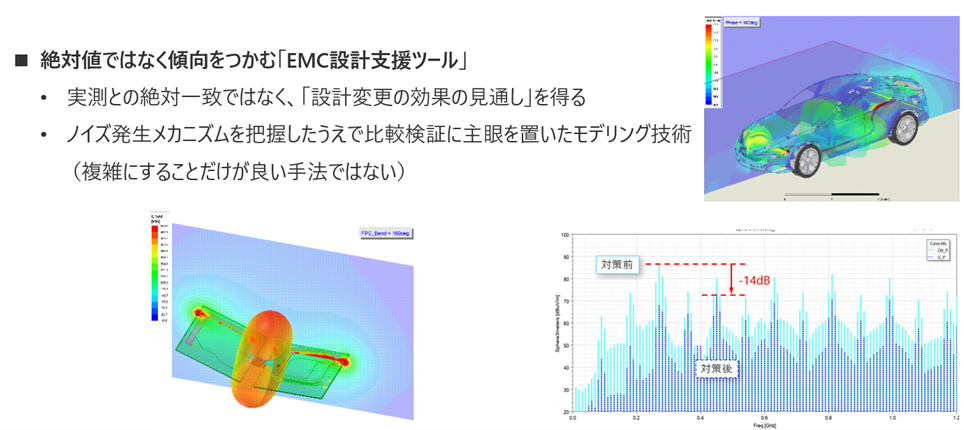

EMC設計におけるCAE活用を現実的に運用するには、期待値の設定が重要です。そこでいったん、解析結果と実測値の絶対値の一致に固執するのではなく、ノイズの発生傾向を正しく捉え、設計変更の効果を比較・検証することに主眼を置いた「現実的なEMC設計支援アプローチ」をお勧めしています。

1.現実的な期待値の設定

EMC解析を、絶対値の一致を目的とした評価ではなく、設計の改善方向を見極めるための「傾向をつかむ解析」として位置づけ、ノイズの発生源や伝搬経路を把握し、「どの対策がどの程度有効か」を予測できれば、設計段階での意思決定に大きく貢献するものと考えています。そこで、ノイズ発生メカニズムの理解を基盤に、比較検証に最適化されたモデリング技術を活用します。モデルを必要以上に複雑化するのではなく、再現性と解析効率のバランスを重視し、設計現場で実際に使える支援ツールとしてCAEを活用します。

現実的な期待値の設定

2.効果的な活用戦略

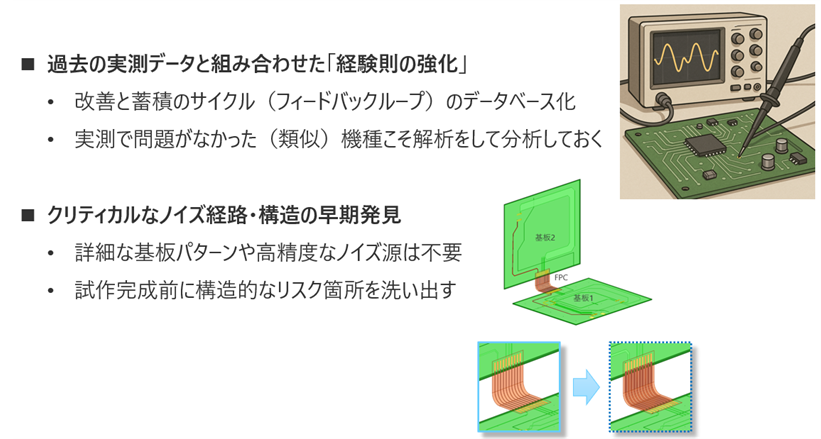

(1)過去の実測データと組み合わせた「経験則の強化」

解析検証は基板や製品の設計段階で実施していくことになりますが、それぞれに対するシミュレーション結果、実施したノイズ対策の手法、あるいは試行したもののノイズ低減に至らなかった手法などを一過性のものとせず、情報として蓄積していくことが重要です。このような取り組みの積み重ねが、EMC設計技術力の向上につながると考えています。

また、実測で問題が認められなかった類似機種についても積極的に解析を行い、「なぜ問題が発生しなかったのか」という要因を分析・整理することで、将来の設計判断に活用できる資産となります。例えば、ある製品に対してシミュレーションを実施し、ノイズ問題が起こりうる箇所を特定したとします。その箇所にノイズ対策を施す際、どの程度の低減を達成すれば実測で問題にならないかという基準を定めることは容易ではありません。このような場合には、実測で問題が生じなかった類似機種のシミュレーション結果を1つの基準(ゴール)として設定することで、効果的なノイズ対策を検討しやすくなるケースがあります。

(2)クリティカルなノイズ経路・構造の早期発見

仮にIDAJでEMC解析を実施する場合は、詳細な基板パターンや複雑なノイズ源をすべて完璧に再現するのではなく、設計上“本質的にリスクの高い箇所”を早期に見極めることに重点を置いています。したがって、解析の対象を、基板・筐体・ケーブルといった主要構造間の電磁結合経路や、共振・ループ形成によってノイズが増幅されやすい部分など、製品のEMC特性における支配的要因に絞り込みます。これにより、過度に複雑なモデルを作成することなく、短時間で設計上の「クリティカル経路」を抽出できるのが特長です。

例えば、FPCやコネクタを介して複数基板が接続される構造では、意図しないリターン電流経路や浮遊容量によって共振が生じやすくなります。このような構造的リスクは、回路図やレイアウトだけでは判断が難しいことが多いのですが、CAE解析によって電磁界分布を可視化することで、結合の強い箇所やノイズ放射の起点を直感的に把握することができます。

効果的な活用戦略

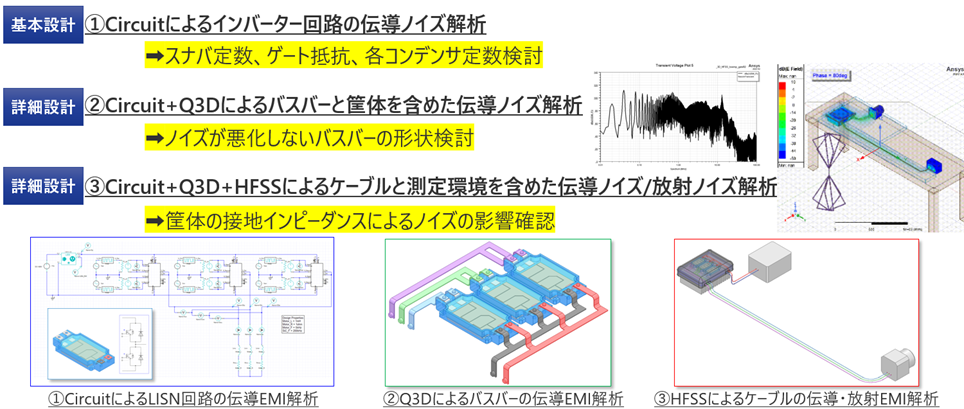

3.インバータのEMI フロントローディングの例

EMC課題を試作段階よりも前の「設計段階」で予測・対策するフロントローディング型アプローチについてご説明します。ここでは、インバータを例に、段階的な解析プロセスによって伝導ノイズと放射ノイズを評価する手法を簡単にご紹介します。このプロセスには、設計の進行度に応じて解析モデルを拡張し、実機試験前にノイズ要因を体系的に把握できるという特徴があります。

(1)基本設計段階:Ansys Circuitによるインバータ回路の伝導ノイズ解析

まず基本設計段階では、スナバ定数やゲート抵抗、各コンデンサの値など、主要パラメータの最適化を目的として、回路シミュレータ(Ansys Circuit)を用いてインバータの電気的挙動を解析し、スイッチング時の電圧・電流波形やノイズ成分の傾向を把握し、初期段階でノイズ発生の支配要因を明確にします。この段階の結果は、後続の3次元電磁界解析モデルに必要な、波形・インピーダンス情報などの入力条件として活用されます。

(2)詳細設計段階①:Ansys Circuit+Ansys Q3Dによるバスバーと筐体を含む伝導ノイズ解析

次に、より詳細な設計段階では、導体形状やレイアウトが寄生インダクタンス・キャパシタンスに及ぼす影響を評価し、ノイズが悪化しないバスバー形状の検討ために、回路解析と電磁界解析(Ansys Q3D Extractor)を連携させ、バスバーや筐体構造を考慮した伝導ノイズ解析を行います。単なる数値比較ではなく、電流経路や共振ポイントを可視化することで、設計者が「なぜその形状が有効か」を理解できるのが特長です。これにより、バスバー設計を電気的観点から最適化し、構造変更前にノイズリスクを最小化することが可能となります。

(3)詳細設計段階②:Ansys Circuit+Ansys Q3D+Ansys HFSSによるケーブル・測定環境を含む伝導/放射ノイズ解析

最終段階では、筐体の接地構造や接続部インピーダンスがノイズレベルに与える影響を評価するために、回路モデルと3D電磁界解析(Ansys HFSS)を統合し、ケーブル配策および測定環境まで含めた伝導・放射ノイズの総合評価を行います。接地インピーダンスの変化がどの周波数帯に影響するかを確認し、実際の測定条件に近い状態でノイズ抑制効果を予測できます。解析結果は、LISN、ケーブル、筐体、負荷モータなどの測定系全体を含めたノイズ経路の可視化として表され、放射経路の特定や効果的な接地手法の検討に直結します。これにより、EMI対策の優先順位を明確にし、設計段階でのEMC最適化を実現します。

このように、IDAJのEMC検証アプローチは、Ansys Circuit・Ansys Q3D・Ansys HFSSを連携させたマルチスケール解析により、回路レベルからシステムレベルまでを一貫して評価できる点に強みがあります。設計初期からノイズ発生メカニズムを可視化し、試作段階での“手戻り”を最小限に抑える―これがIDAJのご提案する「フロントローディング設計」のポイントです。

インバータのEMIフロントローディングの例

IDAJでは、このような複雑に絡み合うEMCと熱の課題に対して、解析技術と設計ノウハウを融合したコンサルティングサービスをご提供しています。経験豊富なエンジニアが、お客様の開発段階に応じた最適なアプローチをご提案し、製品品質の向上と開発効率化をワンストップでご支援します。

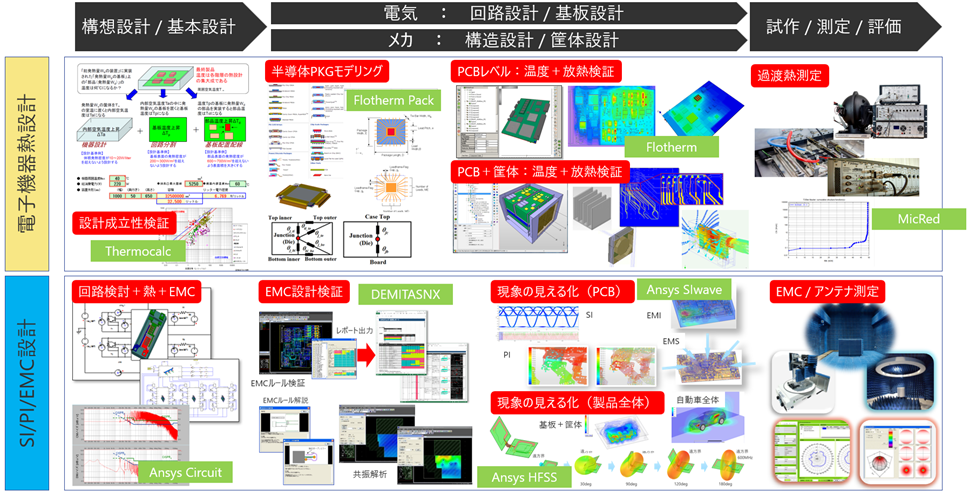

電子機器設計領域におけるIDAJトータルソリューション

■オンラインでの技術相談、お打合せ、技術サポートなどを承っています。下記までお気軽にお問い合わせください。ご連絡をお待ちしています。

株式会社 IDAJ 営業部

Webからのお問い合わせはこちら

E-mail:info@idaj.co.jp

TEL: 045-683-1990